КФ1015ПЛ7 А,Б Предназначена для построения современных экономичных цифровых ФАПЧ синтезаторов частот КВ, УКВ, СВЧ диапазонов. Имеет расширенные функциональные возможности применения в радиоэлектронной аппаратуре. Интерфейс программирования – последовательный, 3-х проводный. Отличается малой потребляемой мощностью и минимизированными весо–габаритными характеристиками. 1. ОСНОВНЫЕ ПАРАМЕТРЫ БИС ( Т=20оС; Ucc1,2 = +5B +- 10%, р абочий диапазон напряжений Ucc1,2 – от 3 до 6В )

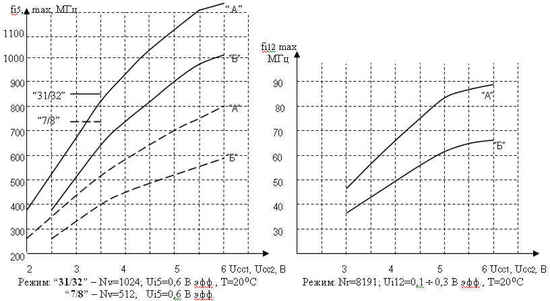

Параметр, обозначение параметра | Значение параметра | Единица измерения | Примечание | Разрядность управляющего слова | 35 | бит | | Диапазоны коэффициентов деления ДПКДv ( шаг 1), Nv1 Nv2 | 49 – 65535 961 – 262143 | ед. | предделитель “7/8” “31/32” | Диапазон коэффициентов деления ДПКДr (с шагом 1), Nr | 3 – 16383 | ед. | | Диапазон рабочей частоты ДПКДv, fiv | 20 – 550 5 – 450 | МГц | “7/8”,группа А (Nv=512) группа Б | 50 – 950 5 – 700 | “31/32”, группа А группа Б | Диапазон рабочей частоты ДПКДr, fir | 0,1 – 80 | МГц | группа А | Максимальная входная частота ЧФД, Fr max | 5 | МГц | | Чувствительность по ВЧ входу ДПКДv, Vi | 0,2 – 0,7 | В эфф. | выше – при fiv =30–200 МГц | Чувствительность по входу ОГ (выв.12) , Vr | 0,1 — 0,15 | В эфф | fir=10МГц | Максимальное напряжение стока NМОS -транзистора, Umax | 12 9 | B | Ids=0,1мА Ids=3мА | Максимальное остаточное напряжение стока NMOS-транзистора, Uds min | не более 0,1 | B | Ids=10мА вывод 15 | Крутизна NMOS -транзистора, S | не менее 40 | мА/В | | Выходное сопротивление ЧФД выходов, Ro | не более 600 не более 220 не более 1200 | Ом | выводы 1, 2 вывод 3 (для Е=1) вывод 3 (для Е=0) | Входные токи низкого уровня, (абсолют.значение) IiL | не более 1 не более 15 | мкА | выводы8,9,10,16 выводы 5,12 | Входные токи высокого уровня, IiH | не более 1 не более 5 не более 15 | мкА | выводы 9,10,16 вывод 8 выводы 5,12 | Ток потребления максимальный ( группа «А»), Icc1 max Icc2 max | 13 | мА | Ucc1=5,5В; fiv=900МГц; Nv=49 | 14 | Ucc2=5,5B, Nv=49, Nr=3, fiv=900MГц, fir=10МГц | Ток потребления в экономичном режиме (группа «А»), Icc1 Icc2 | 3,0 1,1 | мА | Ucc1,2=3,0В; fiv=600МГц, fir=10МГц; Nr=1024;Nv=60000 | Масса (пластмасса, SOР-16, шаг выводов 1,27 мм, планар) | не более 0,3 | г | МS-012 AC | Диапазон рабочих температур, T amb, | — 45…+70 | оС | |

Технические условия Главного конструктора…………………..АДБК.431320.532 ТУ ГК .

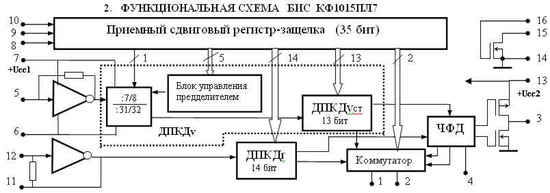

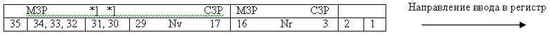

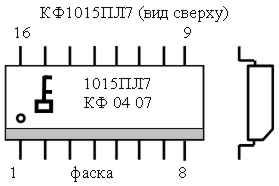

СОКРАЩЕНИЯ: ДПКДv -делитель частоты с программируемыми коэффициентами деления тракта генератора управляемого напряжением (ГУН); ДПКДv ст – старшие разряды общего ДПКДv; ДПКДr — аналогично ДПКДv, но для тракта ОГ(опорного генератора); ЧФД — частотно-фазовый дискриминатор. 3. НАИМЕНОВАНИЕ ВЫВОДОВ 1 – Многофукциональный выход (Фv, Фr, Nv) 9 - Вход тактов записи данных, С 2 — Многофукциональный выход (Фr, Фv, Nr) 10 — Вход данных, D 3 — Выход ЧФД с 3-мя состояниями, pDout 11 — Выход ОГ 4 — Выход контроля захвата ФАПЧ, LD 12 — Вход ОГ, fr 5 — ВЧ вход ДПКДv, fi 13 — Питание +Ucc2 (кроме ВЧ усилителя и предделителя) 6 — Общий 1 (ВЧ усилитель и предделитель) 14 — Общий 2 (кроме ВЧ усилителя и предделителя) 7 — Питание +Ucc1 (ВЧ усилитель и предделитель) 15 — Сток NМОS- интегратора 8 — Вход перезаписи в регистр-защелку, Е 16 — Затвор NМОS — интегратора 4. ФОРМАТ УПРАВЛЯЮЩЕГО СЛОВА  СЗР — старший значащий разряд; МЗР — младший значащий разряд. *] — эти разряды слова игнорируются при выборе предделителя «7/8». Система программирования коэффициентов деления делителей — двоичная. Разряд 35 определяет выбор предделителя: 1 — «7/8»; 0 — «31/32». ДПКДr программируется разрядами 3–16. ДПКДv — разрядами 17–34. Для «7/8»: ДПКДv - 16-разрядный, для «31/32»: ДПКДv — 18-разрядный. При этом разрядность управляющего слова не изменяется — 35 бит. В табл.1 показаны типы сигналов на выв.1 и 2 в зависимости от значения разрядов 1 и 2 управляющего слова. Кроме того, разряд 2 определяет полярность выходной характеристики ЧФД: 1 – негативная, т.е увеличение коэффициента деления Nv (снижение частоты на выходе. ДПКДv) вызывает уменьшение выходного напряжения ЧФД, выв.3 (следовательно, рост управляющего напряжения на выходе интегратора, выв.15). Если разряд 2 – 0, то ситуация обратная, т.е. характеристика ЧФД – позитивная, с ростом Nv напряжение на выв.3 снижается, а на выв.15, следовательно — растет.

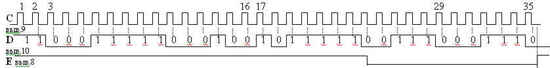

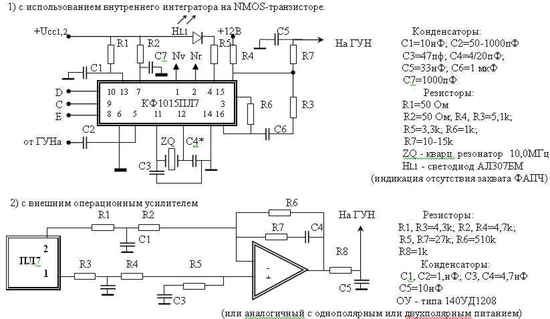

5. ВРЕМЕННЫЕ ДИАГРАММЫ УПРАВЛЯЮЩИХ СИГНАЛОВ  В примере программирования коэффициентов: Nr=1988; Nv=195015 («31/32»). Фиксация данных в каждом разряде приемного регистра - по отрицательным фронтам импульсов С. Лог. уровни сигналов на выв. 8,9,10 — «0»< 0,2 Ucc; «1» > 0,7 Ucc. Частота импульсов С (выв.9) — не более 10МГц. Задержка между отрицательным фронтом С и фронтами D — не менее 15нс. Задержка между отрицательным фронтом С и положительным фронтом Е — не менее 15нс. Длительность фронтов сигналов D, С, — не более 0,5мкс. Информация о Nv и Nr из приемного сдвигового регистра переписывается в регистр-защелку по положительному фронту Е. Длительность положительного уровня Е=“1»определяет продолжительность работы ЧФД, выв.3, в режиме увеличенного выходного тока, т.е. с уменьшенным выходным сопротивлением ключей, а при Е =“0» ключи ЧФД имеют большее сопротивление. Соотношение между большим и меньшим выходными токами ключей ЧФД составляет 5:1. Использование режима с большими токами ЧФД целесообразно для кольца ФАПЧ в период настройки, а на период удержания синтезируемой частоты (синхронизма в кольце ФАПЧ) – режим с уменьшенными выходными токами ЧФД. 6. ОБЩИЕ СВЕДЕНИЯ 1. Обязательно соблюдение правил включения КМОП ИС: напряжение питания подается в первую очередь, после — внешние сигналы (допускается одновременное подключение питания и внешних сигналов), амплитуда которых не должна превышать +Ucc1 и +Ucc2, разность напряжения между +Ucc1 и +Ucc2 не должна превышать 0,5В. 2. При монтаже микросхемы необходимо принимать меры по защите выводов от статического электричества (антистатический браслет монтажника, заземленное жало паяльника с рабочим напряжением 12- 24 В). Максимально-допустимый статический потенциал на выводах БИС — не более 150 В. 3. Пайку выводов БИС выполнять паяльником с рабочим напряжением не более 24 В. Желательно первыми паять выводы 13,14,6,7 в любой последовательности . 4. ОГ на кварцевом резонаторе работает на частоте параллельного резонанса. Конденсатор С4 позволяет подстраивать в узком диапазоне частоту опорного генератора. 5. При работе с внешним кварцевым генератором его выходной сигнал подается на выв.12 через разделительный конденсатор Ср = 1–10нФ. 6. Для контроля коэффициентов деления ДПКДv и ДПКДr необходимо чтобы разряд 1 находился в положении «1». Выходные импульсы отрицательной полярности длительностью (выводы 1 и 2 соответственно): — для Nv: tv1 = 32 * Tвч, предделитель «31/32»; tv2 = 8 * Твч, предделитель «7/8», где Твч - период ВЧ сигнала на выв.5. — для Nr: tr=Тог, Тог — период колебания опорного сигнала. 7. ВЧ сигнал на выв.5 подается через конденсатор Ср = 22 — 500 пФ. 8. В режиме фазового синхронизма петли ФАПЧ на выв.4 — сигнал «1» , светодиод АЛ307БМ не горит, в противном случае — на выв.4 появляется ШИМ – сигнал, который инициирует свечение светодиода.

10. Резисторы R1 и R2 в цепях питания БИС ограничивают сквозной ток в случае тиристорного эффекта (защелки), возникающего только при наличии мощных импульсных помех по входам/выходам или по цепям питания микросхемы. Нестабильная работа ДПКДv может быть следствием слишком большой амплитуды ВЧ сигнала на выв.5. Следует обращать внимание на величину постоянного уровня напряжения на выв.5 без подачи внешнего ВЧ сигнала. Нормальное его значение близко к половине Ucc 1,2. 11. Выв.8 соединен с выводом 6 через внутренний резистор Ri = 1 — 1,5 МОм. 12. Дополнительная маркировка для группы: «А» — красная точка на верхней грани корпуса. 7. ТИПОВЫЕ СХЕМЫ ВКЛЮЧЕНИЯ

— номиналы элементов, приведенных в схемах, подбираются разработчиком синтезатора.

8. СПРАВОЧНЫЕ ЗАВИСИМОСТИ.  .jpg) 9. ЦОКОЛЕВКА И МАРКИРОВКА КОРПУСА МИКРОСХЕМЫ  11. Коэффициенты деления ДПКДv могут быть и меньше указанных значений: Nv1 = 49 (для предделителя «7/8») - 14, 15, 21…23, 28…31, 35…39, 42…47. Nv2 = 961 (для предделителя «31/32») — 62,63,93…95,124…127,155…159,186…191, 217…223,248…255,279…287,310…319,341…351,372…383,403…415,434…447,465…479,496…511,527…543,558…575, 589…607,620…639,651…671,682…703,713…735,744…767,775…799,806…831,837…863,868…895,899…927,930…959. |

| Новости |

|

5 июля 2025

Во втором полугодии 2025г. цены поднимутся на 4%

Подробнее Подробнее

|

|

17 апреля 2025

Нашим потребителям. Согласно своих планов мы планируем на май 2025г. временно прекратить прием заказов на поставку нашей продукции. В апреле и после 31 мая 2025 прием заявок будет действовать в прежнем режиме.

Подробнее Подробнее

|

|

7 января 2025

Сохраняем умеренное повышение цен, около 5,5% на 1-е полугодие 2025г.

Подробнее Подробнее

|

|

10 июля 2024

Цены со второго полугодия 2024г. вырастут на 5% по сравнению с ценами 1-го полугодия 2024г.

Подробнее Подробнее

|

|

12 октября 2023

Повышение отпускных цен произойдет традиционно с началом 2024 года

Подробнее Подробнее

|

|